O Coração dos Dados: Como Funcionam os SSDs e a Física dos Elétrons

Durante quase sete décadas, o som característico de um computador trabalhando arduamente era o som de algo girando. Os discos rígidos mecânicos (HDDs) foram maravilhas da engenharia, com braços metálicos microscópicos movendo-se a velocidades vertiginosas para ler dados magnéticos em pratos que giravam a 7.200 RPM ou mais. No entanto, a mecânica tem um limite físico intransponível imposto pela inércia: um disco rígido, por mais otimizado que seja, sempre levará milissegundos preciosos para mover seu braço físico até o setor exato de um dado. No mundo da computação moderna, milissegundos são uma eternidade. Hoje, vivemos em uma era de silêncio absoluto e performance instantânea, onde os SSDs (Solid State Drives) substituíram o magnetismo e o movimento mecânico pela física quântica e pelo controle preciso do fluxo de elétrons em estado sólido.

Quando você salva uma foto, assiste a um vídeo em 8K ou abre um jogo complexo, você está, sem perceber, manipulando bilhões de partículas subatômicas em escalas nanométricas. Os dados não estão mais "gravados" em poeira magnética; eles estão "aprisionados" em câmaras de silício tão isoladas que podem manter sua carga por décadas sem qualquer fonte externa de energia. Este artigo é um mergulho profundo na jornada que nos levou das fitas magnéticas à memória flash tridimensional, explorando a engenharia brutal e os princípios quânticos que tornam o armazenamento ultra-veloz possível e acessível em 2025. Entenda como o seu SSD é, tecnicamente, uma máquina de física quântica operando silenciosamente dentro do seu bolso.

1. O Floating Gate Transistor: Uma Prisão para Elétrons

No nível mais fundamental, um SSD não possui peças móveis, motores ou engrenagens. Ele é composto por chips semicondutores conhecidos como memória NAND Flash. Dentro de cada um desses chips minúsculos, existem bilhões de "células de memória" que atuam como unidades lógicas. O segredo técnico reside em um componente chamado Floating Gate Transistor (Transistor de Porta Flutuante), uma variante sofisticada do transistor MOSFET que encontramos em processadores comuns. Imagine um transistor convencional como uma torneira eletrônica: você aplica uma tensão na "porta" (gate) e a corrente flui entre a fonte (source) e o dreno (drain), representando o valor binário 1 ou 0. O problema é que, ao desligar a torneira (a energia), o estado é perdido instantaneamente.

O hardware do SSD adiciona uma camada extra estratégica: a Porta Flutuante. Esta é uma camada de silício policristalino completamente cercada por um isolante de óxido de silício de altíssima pureza. Como o nome sugere, ela está "flutuando" eletricamente, sem qualquer conexão metálica direta com o resto do circuito. Através de métodos físicos que veremos adiante, podemos injetar elétrons dentro desta câmara ou removê-los. Uma vez lá dentro, cercados por isolantes perfeitos, os elétrons não têm para onde escapar. Em temperatura ambiente, a teoria sugere que um elétron precisaria de mais de 10 a 20 anos para conseguir sair dessa "prisão", o que garante que seu arquivo não desapareça quando você desliga o computador. A presença de carga na porta flutuante altera o limiar de tensão necessário para o transistor conduzir, o que permite que o controlador do SSD "leia" o valor guardado sem alterar a carga interna.

2. O Milagre do Tunelamento Quântico: Atravessando a Parede

Se a câmara da porta flutuante é cercada por um isolante perfeito, como conseguimos colocar ou retirar elétrons de lá sem quebrar fisicamente o transistor? A resposta não está na eletrônica clássica, mas na física quântica: o fenômeno do Tunelamento Fowler-Nordheim. De acordo com a física clássica, se você joga uma bola contra uma parede sólida, ela sempre volta; mas no mundo quântico das partículas subatômicas, um elétron atua como uma onda de probabilidade. Se a barreira de óxido de silício for fina o suficiente (cerca de 10-20 nanômetros) e aplicarmos uma tensão elétrica precisamente calibrada (em torno de 20V), o elétron tem uma probabilidade real de "aparecer" do outro lado da barreira, atravessando-a como se ela não existisse.

Os SSDs operam baseados nesse comportamento probabilístico. Para programar uma célula (escrever dados), o controlador aplica uma alta tensão na porta de controle, forçando elétrons a "tunelar" para dentro da porta flutuante. Para apagar, o processo é invertido: a tensão é aplicada no substrato do chip, puxando os elétrons de volta para fora da câmara. É fascinante notar que cada vez que esse tunelamento ocorre, a passagem forçada de partículas eletrizadas causa micro-danos permanentes na rede atômica do isolante de óxido. Com o tempo e milhares de ciclos de escrita/apagamento, esse isolante fica cheio de "cicatrizes" e falhas microscópicas por onde os elétrons começam a vazar. É por esse motivo fundamental, ditado pela física de materiais, que todos os SSDs têm uma vida útil finita, medida em ciclos P/E (Program/Erase) ou TBW (Total Bytes Written).

Modelos de SSD mais novos (especialmente os da Samsung e WD) usam uma alternativa chamada Charge Trap Flash (CTF). Em vez de uma porta flutuante de silício condutor, eles usam uma camada isolante de nitreto de silício para "aprisionar" elétrons. O CTF é menos propenso a falhas de vizinhança e permite que os chips sejam ainda mais finos, sendo a base tecnológica que permitiu o empilhamento vertical extremo de centenas de camadas em chips modernos.

3. A Luta pela Densidade: De SLC a PLC

No início da febre dos SSDs, cada célula de memória era binária no sentido mais puro: ou havia uma carga de elétrons (representando o bit 0) ou a célula estava vazia (bit 1). Isso é conhecido como SLC (Single-Level Cell). SSDs SLC são incrivelmente rápidos e resilientes, durando até 100.000 ciclos de escrita, mas são extremamente caros e de baixa densidade. Para colocar mais gigabytes no mesmo pedaço de silício, os engenheiros decidiram que, em vez de apenas medir "cheio ou vazio", poderiam medir a quantidade exata de carga elétrica dentro de cada célula, dividindo-a em níveis microscópicos de tensão.

Assim surgiram as gerações de densidade variável, cada uma trazendo um desafio maior para o controlador:

- MLC (Multi-Level Cell): Guarda 2 bits por célula, exigindo a distinção entre 4 níveis de tensão (00, 01, 10, 11).

- TLC (Triple-Level Cell): Guarda 3 bits por célula, distinguindo entre 8 níveis de tensão. É o padrão de custo-benefício que domina o mercado hoje.

- QLC (Quad-Level Cell): Guarda 4 bits por célula, distinguindo entre 16 níveis de tensão minúsculos. Oferece alta capacidade (SSDs de 8TB acessíveis), mas com durabilidade reduzida de cerca de 1.000 ciclos de vida.

- PLC (Penta-Level Cell): A próxima fronteira, com 5 bits por célula e 32 níveis de tensão. Exige algoritmos de correção de erro (ECC) extremamente potentes, pois qualquer variação mínima de temperatura ou ruído elétrico pode alterar o valor lido.

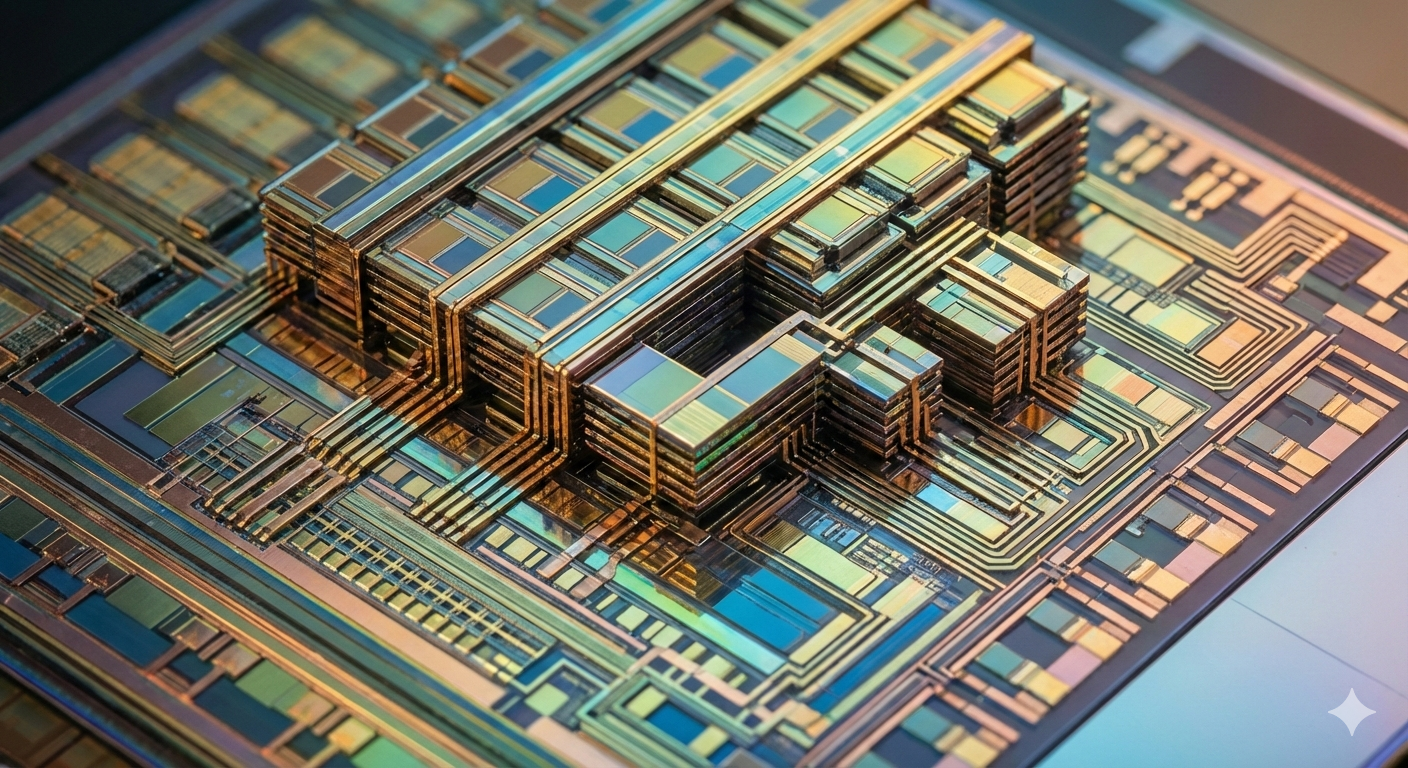

4. 3D NAND e a Era dos Arranha-Céus de Dados

Por volta de 2013, o desenvolvimento planar (em 2D) da memória flash atingiu um muro físico intransponível. As células tornaram-se tão pequenas e próximas umas das outras (abaixo de 15 nanômetros) que o campo elétrico de uma célula começava a interferir nos elétrons da vizinha, um fenômeno chamado de Interferência Celular. Ler um dado tornava-se uma loteria estatística. Para continuar escalando a capacidade, a indústria (liderada pela Samsung com o V-NAND) decidiu parar de tentar apertar as células horizontalmente e começou a empilhá-las verticalmente, como andares de um arranha-céu.

O 3D NAND permite que bilhões de células sejam conectadas através de canais verticais perfurados por lasers e gravuras químicas ultrassensíveis. Hoje, já existem chips comerciais com 232 camadas ou mais de células empilhadas. A verticalização resolveu o problema da interferência, pois as células puderam voltar a ter tamanhos maiores e mais estáveis, enquanto a densidade por milímetro quadrado disparou. Cada aumento no número de camadas exige uma precisão de engenharia digna de nanotecnologia espacial, pois o furo vertical que conecta as células deve ser perfeitamente reto e uniforme através de centenas de filmes finos de materiais diferentes.

Guerra de Arquiteturas: SLC vs TLC vs QLC

| Métrica | SLC (Industrial) | TLC (Mainstream) | QLC (Storage) |

|---|---|---|---|

| Bits por Célula | 1 Bit | 3 Bits | 4 Bits |

| Níveis de Tensão | 2 Níveis | 8 Níveis | 16 Níveis |

| Ciclos de Vida (P/E) | 100.000 | ~3.000 | ~1.000 |

| Velocidade de Escrita | Máxima (Simples) | Média (Complexa) | Baixa (Exige Cache) |

| Custo por GB | Altíssimo | Baixo | Muitíssimo Baixo |

| Principais Usos | Servidores / Militar | Notebooks / Gaming | Backup / Arquivamento |

5. O Controlador SSD: O Maestro da Silício

Se a memória NAND é o "corpo" onde os dados moram, o Controlador é o cérebro que gerencia todo o caos atômico. Um controlador de SSD moderno é, na verdade, um processador multi-core com sua própria RAM (DRAM Cache) executando uma lógica de software extremamente complexa chamada FTL (Flash Translation Layer). O controlador faz muito mais do que apenas mover bits; ele realiza uma logística de proteção constante para que o drive não morra prematuramente.

As funções vitais do controlador incluem:

- Wear Leveling (Nivelamento de Desgaste): Garante que nenhuma célula seja usada mais do que as outras. Se você salva o mesmo arquivo Excel repetidamente, o controlador o escreve em lugares físicos diferentes a cada vez para distribuir o desgaste uniformemente pelo chip de silício.

- Bad Block Management: Identifica e isola células que pararam de segurar carga, movendo os dados preventivamente para áreas de reserva.

- Garbage Collection (Coleta de Lixo): Como a memória NAND só pode ser apagada em blocos grandes, mas escrita em páginas pequenas, o controlador precisa constantemente mover dados válidos de um lado para o outro para "limpar" blocos sujos, um processo que consome poder de processamento interno.

- Over-provisioning: O controlador reserva uma parte da memória (geralmente de 7% a 15% do total) que você nem sequer vê no Windows. Essa área é usada como "respiro" para os processos de reorganização interna de dados.

6. O Protocolo NVMe e o Barramento PCIe

Até pouco tempo atrás, os SSDs eram forçados a usar o protocolo SATA, que foi desenhado nos anos 90 para a mecânica lenta dos discos rígidos. O SATA possui apenas uma "pista" (fila de comandos) que suporta 32 ordens por vez. O NVMe (Non-Volatile Memory Express) rompeu com esse passado. Ele foi criado especificamente para a velocidade da luz do silício, rodando diretamente sobre o barramento PCIe da CPU. Enquanto o SATA é uma rua de mão única e estreita, o NVMe é uma rodovia de 65.535 faixas simultâneas (filas de comandos), onde cada faixa pode carregar 65.535 pacotes de dados.

Com o advento do PCIe Gen 5, os SSDs atingiram velocidades brutas de mais de 14.000 MB/s. Isso é rápido o suficiente para carregar o conteúdo de um DVD inteiro em menos de meio segundo. Essa largura de banda imensa permitiu tecnologias como o DirectStorage, onde a GPU pode puxar dados de texturas diretamente do SSD sem passar pela CPU, eliminando gargalos de processamento e permitindo mundos de jogos vastos e sem telas de carregamento intermediárias.

7. Cronologia Técnica do Armazenamento Digital (1956 - 2025)

- 1956: IBM lança o RAMAC 305, o primeiro HDD comercial. Tinha o tamanho de dois guarda-roupas e guardava 5MB em 50 discos de 24 polegadas.

- 1967: Dawon Kahng e Simon Sze inventam o transistor de porta flutuante (Floating Gate) nos Bell Labs, a base de toda a memória não-volátil.

- 1980: Fujio Masuoka na Toshiba inventa a arquitetura de memória Flash, ganhando esse nome pela rapidez com que as células podiam ser apagadas.

- 1984: Masuoka apresenta o conceito de NAND Flash (E/S paralela) contra o modelo NOR (E/S serial), revolucionando a densidade de dados.

- 1987: Toshiba lança a primeira memória NAND comercial do mundo, iniciando a corrida pela miniaturização.

- 1991: SanDisk lança o primeiro SSD comercial de 20MB para a IBM, custando mil dólares por drive e pesando como um tijolo.

- 1995: M-Systems introduz o DiskOnChip, o primeiro passo para o armazenamento flash embutido no hardware.

- 1999: Inventada a tecnologia MLC (2 bits por célula), dobrando teoricamente a capacidade mundial de armazenamento flash.

- 2003: O padrão Serial ATA (SATA) é introduzido para HDDs, mas torna-se o primeiro gargalo para os futuros SSDs.

- 2006: Samsung lança o primeiro drive de 32GB para laptops, sinalizando o início do fim dos HDDs em dispositivos móveis premium.

- 2008: Intel e Micron anunciam a produção de memórias flash em 34nm, quebrando recordes de densidade na época.

- 2009: Lançado o padrão SATA 3.0 (6 Gbps), atingindo o limite prático de transmissão de dados via cabos tradicionais.

- 2011: Primeira especificação oficial do NVMe 1.0 é lançada por um consórcio liderado pela Intel, focando em baixa latência.

- 2013: Samsung lança o primeiro drive V-NAND (3D) comercial, empilhando 24 camadas e resolvendo o problema da interferência planar.

- 2015: SSDs tornam-se o padrão de fábrica no MacBooks e notebooks premium da Dell e HP, forçando o mercado para cima.

- 2017: Intel lança o Optane baseado em 3D XPoint, uma memória de fase de mudança que prometia latência de RAM com persistência de SSD.

- 2019: Consolidação do PCIe 4.0 em placas-mãe de consumo; SSDs gamers atingem a marca de 5.000 MB/s.

- 2012: Implementação massiva do protocolo NVMe 2.0, permitindo que CPUs controlem zonas de memória de forma inteligente (ZNS).

- 2023: Lançamento comercial dos primeiros SSDs PCIe Gen 5 com velocidades superiores a 12.000 MB/s e necessidade de dissipadores ativos.

- 2024: SK Hynix e Samsung apresentam memórias NAND com mais de 300 camadas e tecnologias de OCP (Open Compute Project).

- 2025: Expansão do Computational Storage, onde o próprio SSD possui núcleos de IA para processar dados antes de enviá-los à CPU.

8. Glossário de Engenharia de Baixo Nível

- NAND Flash: Memória não-volátil que usa portas lógicas do tipo NAND em série, priorizando densidade sobre velocidade de acesso aleatório imediato.

- P/E Cycle (Program/Erase): A medida de saúde de uma célula; representa uma rodada completa de escrita e apagamento via tunelamento quântico.

- FTL (Flash Translation Layer): O software interno que traduz pedidos lógicos do Windows em ordens físicas de bits dentro dos chips.

- TBW (Total Bytes Written): A métrica comercial que indica quantos terabytes você pode escrever no drive antes da garantia expirar.

- TRIM: Um comando que avisa ao SSD quais dados não são mais válidos no sistema operacional, permitindo uma limpeza de lixo mais eficiente.

- ECC (Error Correction Code): Algoritmos que detectam e corrigem automaticamente bits que mudaram de valor devido ao calor ou radiação cósmica.

- Latência: O tempo decorrido entre o pedido de um dado e a entrega do primeiro bit. Em HDDs são milissegundos; em NVMe são microssegundos.

- IOPS: Operações de Entrada/Saída por segundo. Mede a capacidade multitarefa de um drive lendo milhares de arquivos pequenos ao mesmo tempo.

- ZNS (Zoned Namespaces): Tecnologia que permite ao software organizar dados em zonas sequenciais, reduzindo drasticamente o desgaste e o custo de coleta de lixo.

- SLC Cache: Técnica de simular um drive SLC rápido usando células TLC/QLC temporariamente para acelerar pequenas transferências do dia a dia.

Fontes e Referências Profissionais para Estudo Técnico

- Samsung Semiconductor Global. V-NAND Architecture: A Vertical Stack Evolution and physical challenges (Whitepaper 2024).

- IEEE Xplore Digital Library. Fowler-Nordheim Tunneling: Mathematical Modeling and Reliability in 3D NAND architectures.

- Micron Technology Inc. The Science of SSD Controllers: How to manage billions of writes per second without failure.

- NVMe Express Org. NVMe 2.0 Base Specification and Zoned Namespace Technical Reference Guide.

- Western Digital Research. Computational Storage: Moving AI Processing to the Edge of the Silicon (2025 Technical Brief).

- Simha, Sethumadhavan (Columbia University). Computer Architecture: Memory Hierarchies and Flash Storage Fundamentals (Lecture Series).

- Ars Technica Engineering. The Quantum Mechanics of your SSD: How elétrons are trapped in silicon jails.

- Sandisk Professional. Wear Leveling and Garbage Collection: The silent wars inside your storage controller.

- Journal of Solid-State Circuits (JSSC). Single-Slope ADC for high-precision TLC and QLC sensing in NAND memories.

- SNIA (Storage Networking Industry Association). Evolution of Storage Protocols: From IDE to AHCI to NVMe Over Fabrics.

- Toshiba Electronic Devices and Storage Corp. History of Flash: The Legacy of Fujio Masuoka and the birth of a Trillion Dollar Market.

- Intel Labs. The Future of Phase Change Memory and Persistent RAM: Challenges after 3D XPoint.

- SK Hynix Newsroom. Achieving 321 Layers: The next frontier of vertical density in semiconductor manufacturing.

- Phison Electronics. Designing Gen 5 SSD Controllers: Heat Management and Data Integrity at 14GB/s.

- Hacker News Archive. Debates on Reliability: Is PLC (Penta-Level Cell) the death of long-term storage?.

- Tom's Hardware. SSD Benchmarks: Real world performance impacts of DRAM-less vs DRAM-equipped drives.

- California Institute of Technology (Caltech). Semiconductor Physics: Tunneling effects in Nanoscale Transistors.

- Crucial Technology. A Buyer's Guide to NAND Durability: Understanding MLC, TLC, and TBW ratings.

- AnandTech. Inside the Controller: How Wear Leveling algorithms extend drive life by a decade.

- Nature Materials. New Isolators for Charge Trap Flash: Beyond Silicon Nitride for 1000-layer chips.

- Microsoft Learn. DirectStorage API: Accelerating Game Loading via NVMe and GPU direct memory access.

- Dell Technologies. Enterprise Grade Flash: What distinguishes a data center SSD from a consumer drive.

- Oracle Engineering. Optimizing Databases for NVMe: How to handle 1 million IOPS per server node.

- Journal of Vacuum Science & Technology. Atomic Layer Deposition (ALD) in the manufacturing of 3D NAND structures.

- Phys.org. Observing Electron Tunneling in real-time within experimental memory cells.

- PCWorld Technical Archive. The transition years (2010-2015): How SSDs saved the declining PC market.

- Zacks, R. Solid State Revolution: The engineers who reinvented human memory at the speed of electricity.

Artigo elaborado por Mão na Roda, focado na intersecção entre física de semicondutores e arquitetura moderna de computadores. Revisado em Dezembro de 2025.